石英晶振是电子产品不可或缺的一部分,它的振荡频率可确保电子产品稳定有效的运行,但是石英晶振的生产设计并非想象的那么简单;虽然随着电子产品市场需求的一再提高,但各大晶振厂家从未停止前进的脚步,都在竭力生产能够适应市场需求的产品;在石英晶振中晶振电路又是主要核心部分,那么应该怎样设计晶振电路呢?又有哪些是需要注意的?且待下文详解.

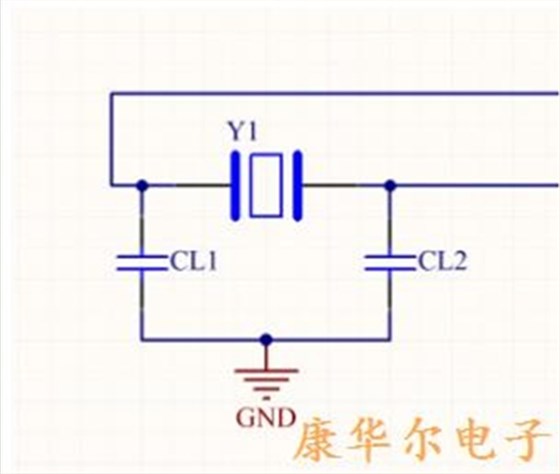

晶振从性能上可以分为有源晶振和无源晶振;不管是有源晶振也好还是无源晶振也罢,晶振产品都可以等效为一电容和一个电阻并联之后再串联一个电容的二端网络;而晶振电路就是在一个反相放大器的两端接入晶振,再在晶振的两端接入电容,电容另外一端接地就行.怎么样,看起来是不是很简单,但是想要设计一个晶振电路可并不容易:下面就晶体振荡器电路来说明设计流程以及详情介绍.

图1:基本晶体振荡器电路

电路设计过程

四个简单的步骤:

1,选择水晶

2,检查微控制器是否可以驱动晶振

3,晶体可以处理功率损耗吗?

4,选择负载电容CL1和CL2

第1步:选择一个水晶

你已经知道你想要什么样的水晶.稍后将讨论不同晶体之间的权衡.选择一个适合您需求但不太贴切的,您可以尽快重新审视这一步.

第2步:检查微控制器是否可以驱动晶振

微控制器数据表为有源石英晶体振荡器选择提供了一些指导.这些参数与临界增益有关.临界增益是微控制器电路启动晶体振荡器所需的最小增益.

对于给定的一组频率和负载电容,一些微控制器数据表提供了晶体允许的一组最大ESR.

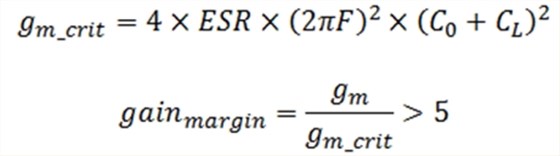

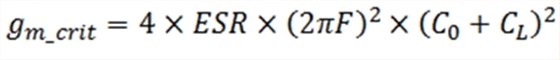

如果微控制器数据表提供振荡器跨导(通常为uA/V)或最大临界增益,那么我们需要计算晶体的临界增益并检查微控制器是否可以驱动它

其中:

-F是晶体的标称频率

-ESR是晶体的等效串联电阻

-C0是晶体分流电容

-CL是晶体的标称负载电容

关键增益是晶体的特性,这些参数在晶体的数据表中.

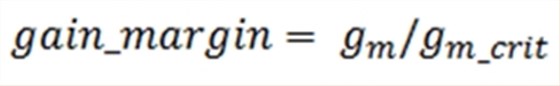

接下来计算增益余量.如果增益裕度大于5,则振荡器将可靠地启动.增益裕度越大意味着振荡器启动越快.

或者,一些微控制器数据表提供最大临界增益gm_crit_max.在这种情况下,gm_crit必须小于gm_crit_max.

如果微控制器不满足驱动晶体的要求,则选择另一个晶体.

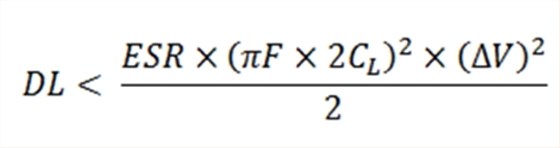

第3步:晶体可以处理功率损耗吗?

数据表中规定了贴片晶振的驱动电平(DL).驱动电平基本上是正常工作时晶体的最大额定功率.

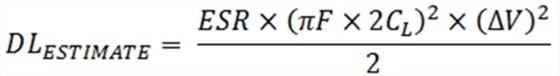

DL的粗略高估可以如下计算:

其中:

-ΔV是峰峰值振荡器电压-使用最坏情况:ΔV=Vcc

如果估算低于晶振的额定驱动电平,则转到最后一步.如果估计值高于晶振的额定驱动电平,您可以优化估算值(稍后参见示例)或选择另一个晶体并再试一次.

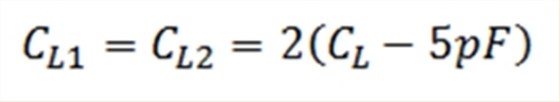

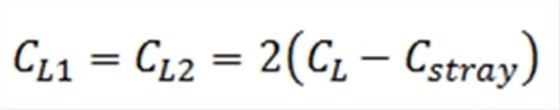

步骤4:选择负载电容CL1和CL2

负载电容将晶振调谐到正确的频率.

我第一次设计晶体振荡器电路时,我假设两个负载电容并联连接.我选定的CL1=CL2=0.5*C大号.我的同事假定是cL1=CL2=C大号.这两种选择都很常见.两者都错了.

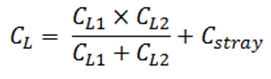

负载电容是石英晶振上所需的电容,因此CL1和CL2串联连接.

我想将其简化为:

C杂散是微控制器引脚和走线电容的杂散电容积累.许多应用笔记建议估计此值约为5pF.一些微控制器数据表提供了有关该值的更准确数据-例如,msp430f22x2系列指定1pF的杂散电容,这与其低功耗模型非常吻合.如果您的微控制器数据表没有此信息,请将C杂散估计为5pF.

可见一个基本的晶振电路的构造相当简单,但是附带许多性能的晶振电路就比较复杂,只是在这个基础构造上添加一些能够实现特殊功能的电路,但大都殊途同归.在设计晶振电路的过程中最主要的就是电容的匹配,SMD晶振有一个十分重要的性能指标,那就是负载电容,这是衡量石英晶振产品性能优劣的指标之一,我们只有选择与负载电容一样值的并联电容才能得到晶振标称的谐振频率.

京瓷晶振,时钟振荡器,KC7050A-C1晶振,7050有源晶体

京瓷晶振,时钟振荡器,KC7050A-C1晶振,7050有源晶体 京瓷晶振,热敏晶振,CT2016DB晶振,CT2016DB38400C0FLHA2晶振

京瓷晶振,热敏晶振,CT2016DB晶振,CT2016DB38400C0FLHA2晶振 京瓷晶振,热敏晶振,CT1612DB晶振,CT1612DB38400C0FLHA1晶振

京瓷晶振,热敏晶振,CT1612DB晶振,CT1612DB38400C0FLHA1晶振